谁会愿意天天用一个课六个字的全名来叫它呢,但是数字逻辑电路是数电,数字逻辑设计是数设,数字逻辑实验总不能是 /数[字逻]?实验?/,但叫它数电实验或者数设实验好像都不太对,草(

上课的时候也是,老师一会儿一个“如果你是数设的同学”,一会儿一个“如果你没报上数设但想把数电学成数设”,这课也太乱了(

我写游记都得把两个课放一起写,课就不能合成一个吗(

写了一会儿后发现,还是得两个课分开写,dbqwcl(

这篇就是个游记,具体学的内容如果我有时间的话会放在 DDPP 学习笔记,没时间(没时间写笔记 or 没时间学 DDPP 只能跟着上课)的话大概就不会放上来了(

某些人学都学不完了,还有空写游记?(

数字逻辑实验

sv 班的开设

DDPP5 讲的是 Verilog,以后造机应该也是用 Verilog,但数字逻辑实验似乎是 VHDL。就像软工强迫我把技术栈全换一遍一样,多学一门语言也可以称作“技多不压身”,而且说到底我也还没学 Verilog(,但终究是有些难受的。所以看到第一节课的课件上说可以选择报 SystemVerilog 小班我还是很开心的,顿时感觉这个课科学了许多(

优势:对后续课程有帮助

劣势:花时间,费精力。。。

课件上是这么写的,但 Verilog 本身应该不会比 VHDL 费精力,课程内容的区别是多了个内存实验,我猜这个 warning 的主要意义在于,这是个新开的课,可能各种出锅,要让大家做好心理准备(同样是新开的 Rust 就非常科学(起码完全自学人感觉很科学),我似乎反而更希望课是新开的,而且这个 sv 班似乎也是 tuna 群友当助教(

但这个 sv 班的开设实在是有些坎坷,说起来也有些冗长,就折起来了。

sv 班课程文档

本课程只有一学分!!

开头第一句,绷不住了(

按钮详细功能

一般来说 admonition 经常是比较长的会折叠起来防止刷屏,但在示波器的“按钮详细功能”一节,被折叠的都是最短的那些,比如:

非常地理所当然,但感觉这个事实莫名地很有意思(而且把电源开关写出来再折起来就莫名喜感(按一次打开 <details>,再按一次关闭 <details>

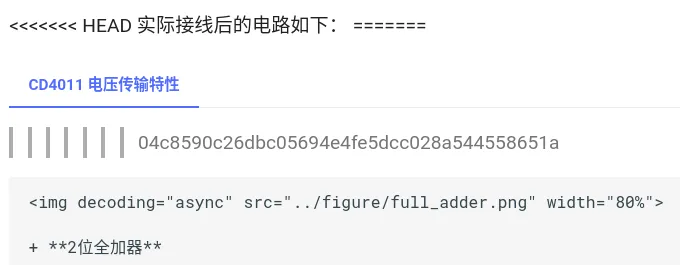

git conflict

虽说是敏捷开发课程文档,但这个 git conflict 也太(

把人忽悠进来之后

下面是两个课件的 diff,虽然这个优势的意思实际上没变,从 sv 班苛刻的开设条件基本上就能猜到没法随时退出,但是(

- SystemVerilog

- 为后续课程实验提供支撑

- 增加内存实验

,其他实验不变- 课程成绩不与普通课堂区分,评分标准,比例与普通课堂一致

- 优势:

对后续课程有帮助当前学期无- 劣势:花时间,费精力。

。。- 可随时退出?

示波器实验

上学期物理实验用过示波器,感到了这个课除了 学习 TeX 和 R 之外竟然还稍微有点用,虽然也只有那么一点点用,不知道和电子学基础相比哪个的一点点大一些(

整个实验中卡壳最久的一步是,从一坨绑得十分整齐的导线中抽出一根,草(

与非门电路测试实验

预习的时候对着文档里的电路图和芯片引脚图把怎么接线、怎么接地写清楚,就很容易了。

本来想半小时速通,失败了,感觉最大的问题还是抽不出导线(

简单组合逻辑电路实验

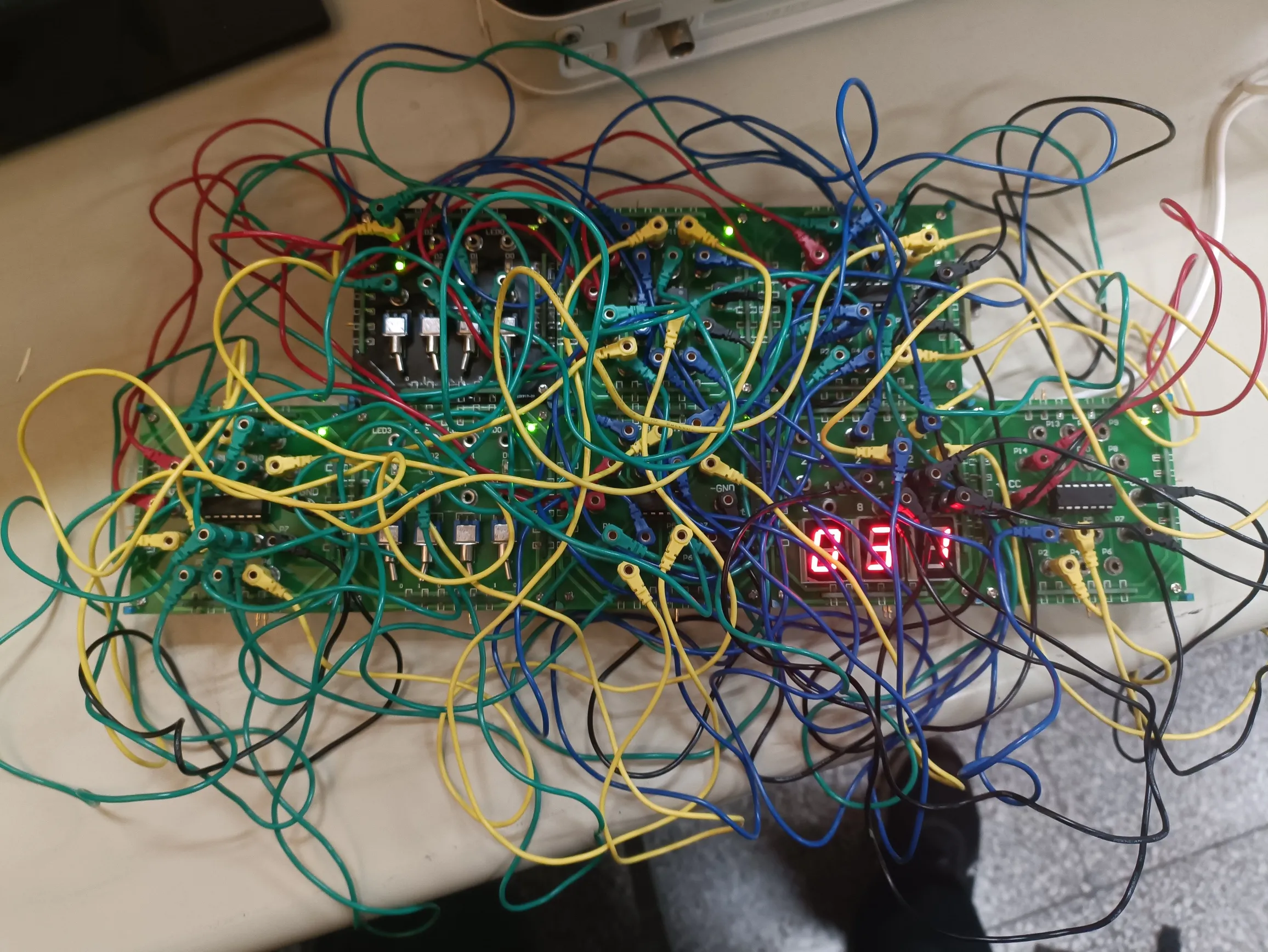

上午十点半才开始预习,两小时把 2 位全加器和补码减法器接好了,在课上半个小时把原码减法器接好,但是加上排队等待验收和收拾东西还是快 3 点才走。

- 三个运算器放在同一个电路里是非常容易的。补码减法器就是全加器的基础上有几个东西要取反,只要把一个开关和这些东西异或在一起就可以控制是否取反了。原码是在补码的基础上进行转换,用开关控制会稍微麻烦一些,但如果是用两个数码管分别显示补码和原码就非常容易。

- 文档上给的补码转原码不知道为什么用了五个门,实际上只要 就好了。

(一开始我还对着卡诺图发呆,后来看了一眼真值表,发现这个东西用人类智慧一下就化简出来了。)最后三合一的电路我只用了 8 个与非门和 9 个异或门,就不需要用 16 pin 的模块了。 - 如果是分步骤(模块)接线(比如先接全加器,再改成减法器),过程中需要改线,在两根线叠在一起时,最好是把“模块内部”的线放在下面,和“外部”连接的线放在上面,这样的话修改和外部的连接时不用把两根线一起拔掉。

- 把接好的线带到实验室是有一定难度的,可以先只接 6 个模块,就能放进实验箱了,课上接剩下的两个模块。接上线之后体积会变大,可以把用不到的模块留在寝室。

(这节课上还发了 FPGA 模块,为了能装下,大家都上交了一些多余的模块,我装得下而且本来就是把多余的放在寝室了,就没上交;但是这样一来我就长期有几个模块放不进实验箱了 🌚)

如果你不知道怎么接线的话可以尝试对着下面这张图复刻

后来看到有同学上面的线统一朝上,下面的线统一朝下,就整齐一些。

最后收拾东西的时候分三次发现地上掉了 5 根线,除此之外前后两排也能看到好多根线,不知道哪些是我的,哪些是隔壁的,哪些是上午的(

还听到助教吐槽同学,然后老师说,这都是正常的,现在我们去搞大模型就可以了,不用在意数电(

点亮数码管实验

本来想在寝室搞完直接去验收,结果去搞智能体了(

现场才开始做,一直连不上芯片,还以为是因为我用的 Arch 所以驱动有什么神秘问题,到处查了半天,最后问老师才知道是我 USB Type C 的线没插紧,绷不住了。它这个接口比一般的手机充电线要紧一些(插上一次之后复现不出来了,但在我印象中插上第一次之前不是紧一点而是紧 super 多),插进去一半灯就亮了,所以我还以为接好了。后来想起来数设课上还提到过,USB 为了支持热插拔,电源接口比数据接口略长一些,我看到的灯大概是电源线连上了的灯,而数据线还没连上。

最后速通彻底失败了,还是第一次做到只剩几个人了才走。

四位全加器实验

这次真的在寝室 1.5h 搞完直接去验收,成功在上课之前验收完了,但还是得听完课才能走(

于是干脆写完了实验报告才走,实际上只是把代码复制出来,再截几张图,不知道为什么没能在讲完课之前写完(

计数器实验

这次有好几个人课前查,助教表示我们太急了(

之前感觉 DDPP 第五章学了几年都没学完(,但有点像当时 CS:APP 第三章,学一周能顶上课讲好几周(

串行密码锁实验

感觉 undefined behavior 非常多,而且作为一个密码锁竟然能在没开锁时改密码,非常神秘,但它毕竟只是个小实验而不是数设(

上课前同学聊到了游泳课,老师一进来听到了,说当年他有个同学因为游泳没过没能保研,但是现在开公司,过得比他爽,绷不住了(

听说助教因为昨晚答疑到太晚,今天没吃早饭,早八还一直搞到 11:30,还蛮惨的。下午助教是准点到的教室,于是没能在课前查完,但其实一讲完课就查也没差太多。

老师:你们是不是觉得提高要求就是必做的?明年干脆把提高要求取消了,解决不了问题可以让问题消失(

耳机线收纳测验

40min 速通了考试,但考完上交实验箱,收拾了半小时导线,成了最后几个走的(

真不懂线为啥要捆起来,白费力气,到时候抽出来也麻烦(

数设

数设第二次课

这节课讲了一堆数电背后的模电原理,而且还是 TTL 电路,不是 DDPP5 放在第 14 章的 CMOS。感觉完全没听懂,只不过说到底这一节是物理课不是计算机课(,后面又说讲的大部分东西不考,讲这些是为了补充一些数字电路发展的历史,弥补思维上的跳跃。

我是完全没听懂,其他同学大概也是没完全听懂。老师吐槽说,现在我们培养方案里电路知识几乎为零,数设要从头开始讲,不像他们那时候,本科上五年,什么物理都学了。本来我还在想,为什么我们只能上四年甚至三年,要学这么多东西,结果老师说他五年修了双学位 600+ 学分,而且学分是和现在一样的学时,震撼全班。

数设与数电

在软工课上被数电同学问了作业,先是被问了没学清楚的,后面又被问了数设没讲的内容。没想到这么早就体验到了被数电同学问懵(

关于 DDPP

其实我开学后有看一点 DDPP,感觉还是比上课讲的科学许多(比如说上课的时候去写软工了,课后看一下 DDPP 会感觉比上课讲的易懂很多,比中文教材易懂 super 多),但没有从头到尾看全,也没写笔记。一方面是时间都被软工占了(,还有就是 DDPP 和上课讲的内容多少有一些差异,要是学多了感觉会搞混(

考前

《我怕你们都考 100 分学校找我麻烦》

《实验做的最好的两个组直接 A+,就算考试交白卷都还有拿 A+ 的机会》

《不要 15min 就做完了》

考试

难度还好,有一题的题意理解有点神秘,但老师说只要能说得通都算对 🤔 考完大家都在吐槽一个考课件细节的填空题(分不多),幸好我是上午刚看的课件,要是前一天看的估计就不会做了(

第一次实验课

这次又在连上板子这一步出了问题,又是线的问题,但幸好不是没插好,而是线真的坏了(

成功把 VGA 显示的样例跑起来之后就开始啥都不懂但是魔改参数,很难不想起小学第一次去上机器人课的时候也是这样(

不能把板子带回寝室,要在板子上调都得跑来东主楼,稍微有点难顶(

《不要在实验室过夜》,绷不住了(

折腾外设

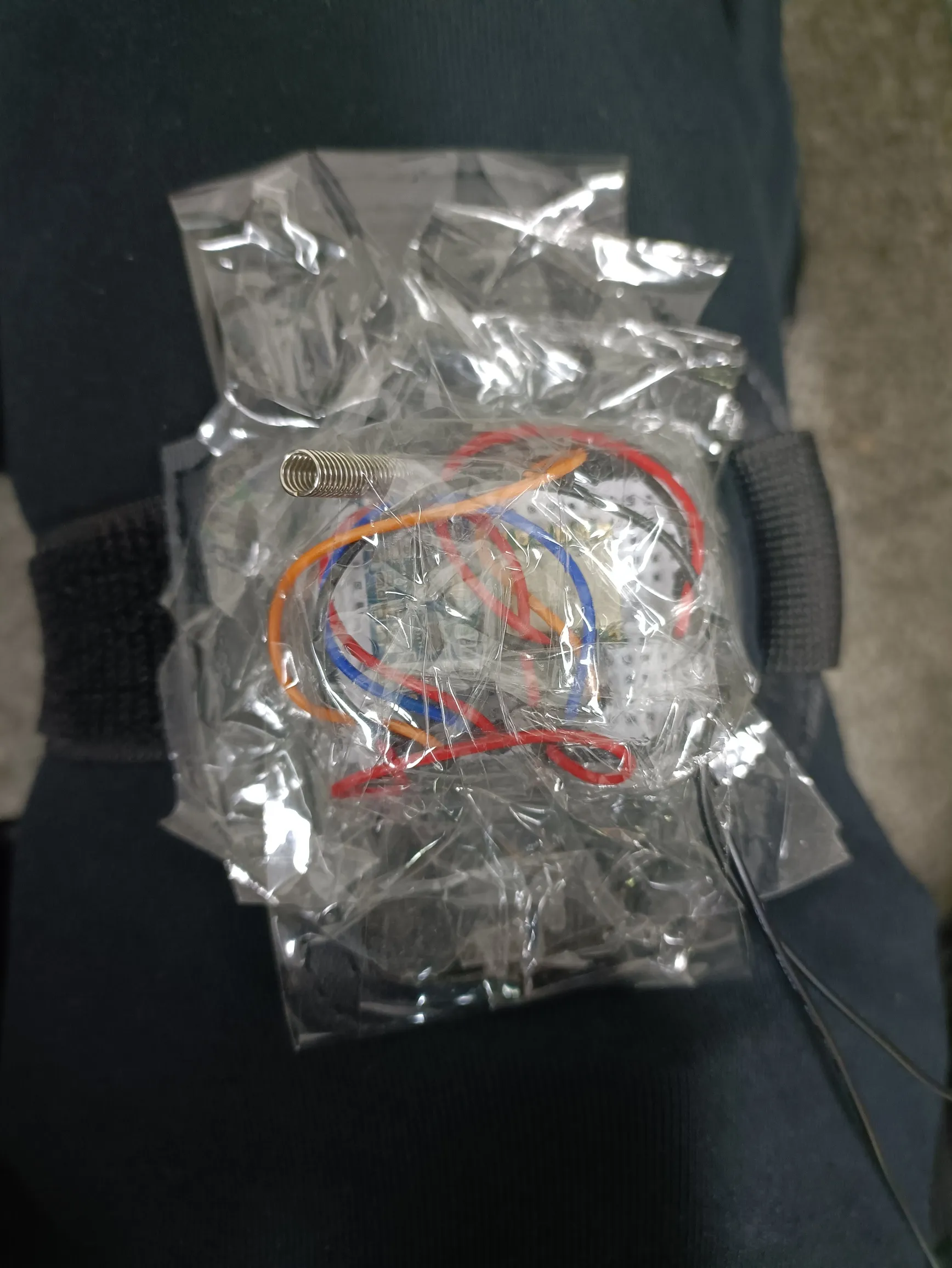

background:我们组想做的是腿部动作控制(类似健身环)的 Chrome 小恐龙。

外设太难了,下次让我选一定只用键盘(

一开始先是排针没焊接,接触非常不良(几乎没有),等到五一结束老师回学校了才焊。老师帮忙焊了一个,让我自己焊了剩下两个,结果焊了三回 啊三回 才焊好。yysy 要是能有一些电子垃圾用来练手的话,还挺简单的,但直接在生产环境上练习实在是有点可怕(

然后是 USB 转 TTL 模块忘接地了,毕竟它不用连电源,于是就忘了(

最后是纽扣电池电流太小,带不动传感器和无线模块,还是只能换成充电宝供电,纽扣电池、电池盒、稳压模块通通白买了(

说起来还挺简单的,但要发现问题在哪真的好难,一会儿怀疑模块烧了,一会儿怀疑是面包板不行,一会儿怀疑是线不行,发现是带不动了还以为是电压没到 3.2V,还得查各个模块的规格,以及想到去查纽扣电池的规格。

最后终于调通了,试着绑在腿上跑跑跳跳,看着凌乱的数据图,还是决定放弃跑动的检测以及跳跃高度的计算,只保留固定高度的跳以及下蹲,有时间再说(

连到板子上时还遇到一个神秘的坑,Pmod 接口有编号为 1~12 的接口,其中 5、6、11、12 是电源和地,1、2、3、4、7、8、9、10 分别是 IO0~IO7,结果我以为 1 是 IO1,调了半天,绷不住了(

来张图:电源的四根线的颜色请不要在意)

这个连接就非常不稳定,跳几下就会松,抚摸 一下这些线就又好了,过段时间还得按一下充电宝开关,之后再看怎么解决。

UPD:每次都要抚摸实在是太不乖了,给它捆绑了一下就老实多了(( 虽然这么开玩笑,我其实挺讨厌捆绑的,哪怕是二次元捆绑图也生理上就感到厌恶,这是可以说的吗

UPD2:刚绑上的时候还挺好的,过了几天又寄了。

UPD3:最后还是焊上了,永远不要相信没有焊上的连线(

调教 VGA

时序好难调(

Quartus 报的时序错误不要无视。

时钟频率太高容易寄,可以调低点。

信号跨域要处理好。

如果信号偏了两三个周期,不用管它为什么会偏,把它偏回来就行(

尽量不要用组合逻辑输出,可以加个 buffer。

展示

最后一天改 slide 的时候一大半的时间花在了 p 这个图标,好想用 StyleDrop(

(这是个 <iframe>,可以翻页)